| Half Adder - Structural Verilog Desig                                  | 'n |

|------------------------------------------------------------------------|----|

| module ADD_HALF (s,c,x,y);                                             |    |

| output s,c;                                                            |    |

| input x,y;                                                             |    |

| wire s,c,x,y;<br>// this line is optional since nodes default to wires |    |

| xor G1 (s,x,y); // instantiation of XOR gate                           |    |

| and G2 (c,x,y); // instantiation of AND gate                           |    |

| endmodule                                                              |    |

| July 8, 2009 ECE 152A - Digital Design Principles                      | 17 |

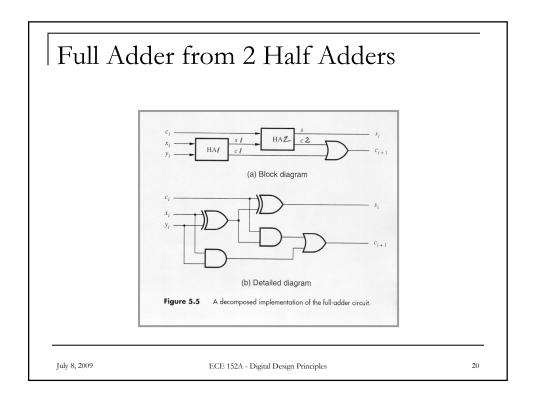

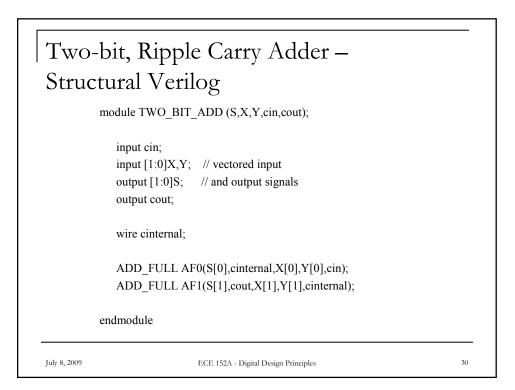

| Full A       | Adder – Structural Verilog Desig                                                 | 'n |

|--------------|----------------------------------------------------------------------------------|----|

| r            | nodule ADD_FULL (s,cout,x,y,cin);                                                |    |

|              | output s,cout;<br>input x,y,cin;                                                 |    |

|              | <pre>//internal nodes also declared as wires wire cin,x,y,s,cout,s1,c1,c2;</pre> |    |

|              | ADD_HALF HA1(s1,c1,x,y);<br>ADD_HALF HA2(s,c2,cin,s1);<br>or (cout,c1,c2);       |    |

| e            | endmodule                                                                        |    |

| July 8, 2009 | ECE 152A - Digital Design Principles                                             | 21 |

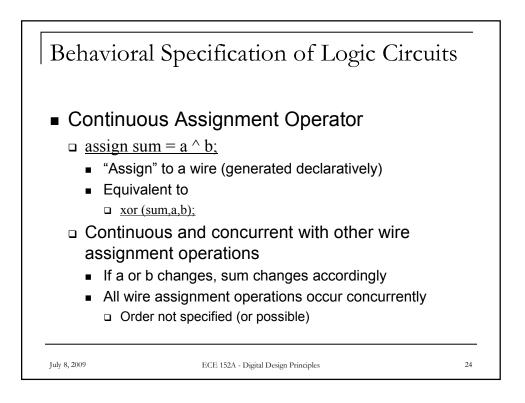

| Full Adder from Logical Operations                  | _  |

|-----------------------------------------------------|----|

| <pre>module ADD_FULL_RTL (sum,cout,x,y,cin);</pre>  |    |

| output sum,cout;                                    |    |

| input x,y,cin;                                      |    |

| //declaration for continuous assignment             |    |

| wire cin,x,y,sum,cout;                              |    |

| //logical assignment                                |    |

| assign sum = $x \wedge y \wedge cin$ ;              |    |

| assign cout = $x \& y   x \& cin   y \& cin;$       |    |

| endmodule                                           |    |

|                                                     |    |

|                                                     | —  |

| July 8, 2009 ECE 152A - Digital Design Principles 2 | 25 |

| Full Adder     | from Arithmetic Operations              |

|----------------|-----------------------------------------|

|                |                                         |

| module ADD_FU  | ULL_RTL (sum,cout,x,y,cin);             |

| output sum,c   | out;                                    |

| input x,y,cin; | :                                       |

| //declaration  | for continuous assignment               |

| wire cin,x,y,s | sum,cout;                               |

| // concatenati | ion operator and addition               |

| assign {cout,  | $sum\} = x + y + cin;$                  |

| endmodule      |                                         |

|                |                                         |

| July 8, 2009   | ECE 152A - Digital Design Principles 26 |

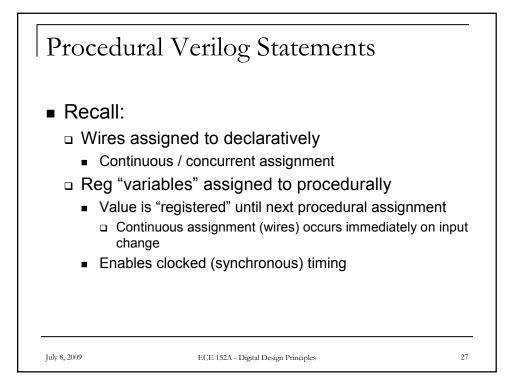

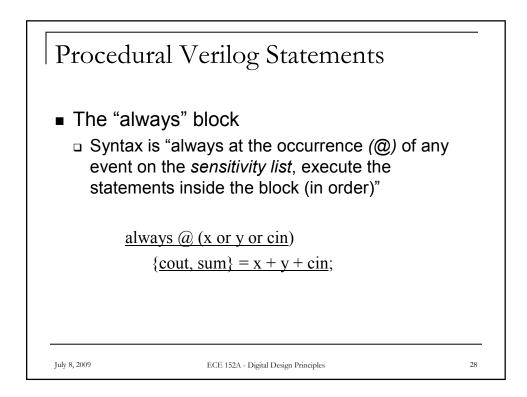

| RTL Design of Full Adder                          |    |

|---------------------------------------------------|----|

| module ADD FULL RTL (sum,cout,x,y,cin);           |    |

| nodule <i>NDD_</i> 10EE_KTE (sun,cout,x,y,cm),    |    |

| output sum,cout;                                  |    |

| input x,y,cin;                                    |    |

| //declaration for behavioral model                |    |

| wire cin,x,y;                                     |    |

| reg sum,cout;                                     |    |

| // behavioral specification                       |    |

| always @ (x or y or cin)                          |    |

| ${\text{cout, sum}} = x + y + \text{cin};$        |    |

| endmodule                                         |    |

|                                                   |    |

| July 8, 2009 ECE 152A - Digital Design Principles | 29 |

| ample                                       |

|---------------------------------------------|

| egin                                        |

| a = -a;                                     |

| egin<br>0 b = $\sim$ b;                     |

| egin                                        |

| $0 \operatorname{ci} = -\operatorname{ci};$ |

| JLL AF1(sum,co,a,b,ci);                     |

| le                                          |

|                                             |